Pico5G Advanced IoT Tester

One Of The Most Advanced 4G/5G IoT Device Tester In The World

Easy-to-use testing tool for 4G/5G cellular technology

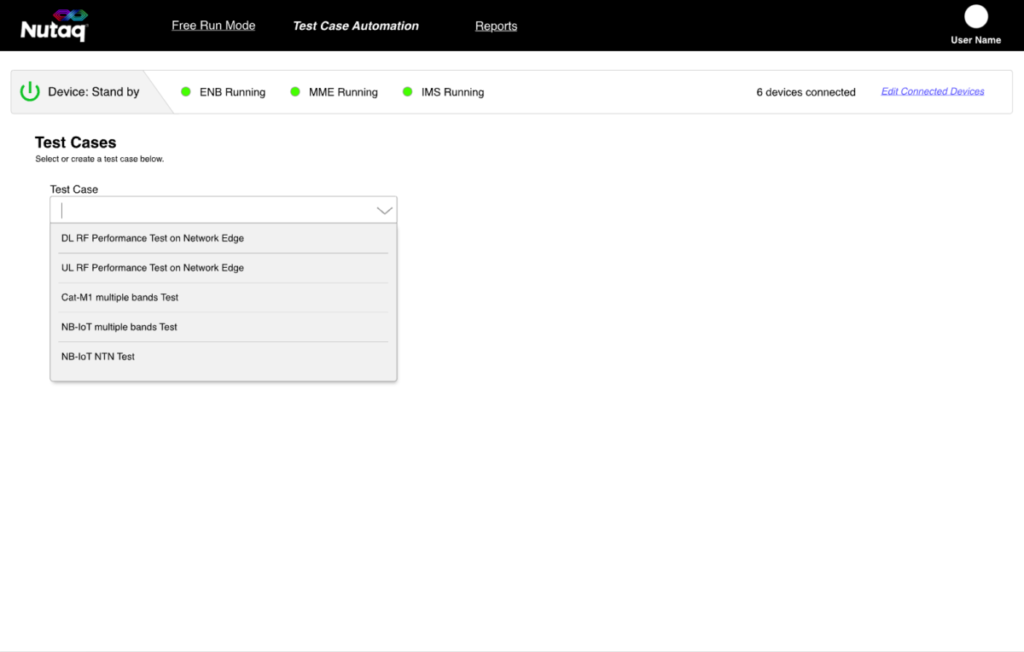

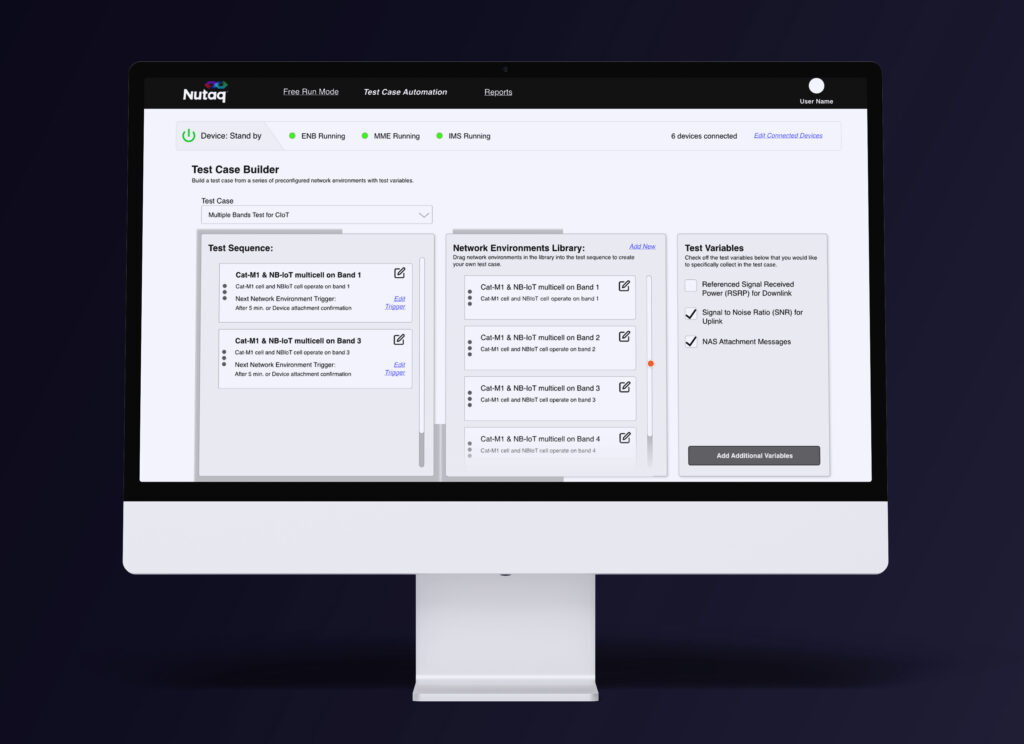

No need to be a telecom expert: With its intuitive GUI and pre-configured test cases, the Pico5G Advanced IoT Tester is easy to use for users of all skill levels. Operated from an intuitive graphical interface with advanced measurement, automation, and scripting capabilities, the Pico5G Advanced IoT Tester includes a complete and fully configurable 4G and 5G network, making it the most versatile and easy-to-use testing tool for your IoT devices.

Key Features

Test your IoT device at every step of the way, without leaving your desk.

User-Friendly Interface

Use an intuitive GUI with pre-configured test cases and network profiles.

Multi-Network Testing

Test multiple devices on 4G (LTE, LTE-M, NB-IoT) and 5G networks concurrently.

Scenario Simulation

Create and playback scenarios, such as an IoT device moving between cells or countries.

End-to-End Connectivity

Test end-to-end connections between your IoT devices, applications, and services over the Internet.

Certified Device Testing

Run standardized test cases for IoT end devices, such as TRP and TRS, according to ETSI specifications, and pass certifications on the first attempt.

Early Access to 3GPP Features

Have early access to 3GPP features to rapidly validate features under development (3GPP release 17 currently supported).

Battery Life Analysis

Characterize IoT device battery life: Record IoT device power consumption profile and battery discharge profile.

Typical Test Cases

Connectivity

- Test connectivity on home and roaming networks

- Detect attach acknowledgement/rejection and IP address assignation

- Test all frequency bands and transmission modes

- Test device behavior in real-world conditions (intermittent connectivity, packet loss, network bandwidth variance, S1/X2 handover)

Power Consumption

- Analyze power consumption granularly and in real-world conditions

- Apply cell RSSI variances

- Apply intermittent connectivity/packet loss

- Enable wake-up command by device and by tracking area update (TAU) parameter expiration

- Activate/disable PSM

- Change eDRX cycle values

Radio Link Performance

- Analyze throughput, latency, and packet loss in real-world conditions

- Control RSSI and bandwidth

- Test all frequency bands and transmission modes

- Enable/disable coverage enhancement and repeating transmission

- Use radiated and conducted measurements

EMC

- Measure electromagnetic interference in real-world conditions

- Control the device transmission power

- Transmit real payload

Get a Quote

Document Detail

Aenean laoreet nunc eget est ultricies faucibus ultricies facilisis.

Get in Touch

We are here to help, feel free to reach out and we’d be happy to assist.

Phone Number

+1 (581) 316-0347 Toll Free 1 888 665 1375 (US and Canada)

Comprehensive Testing Solutions for IoT

Our goal is to help businesses launch innovative products with confidence by providing advanced testing solutions and expert support.